Без рубрики

Расширяемая ISA с открытым исходным кодом RISC-V набирает обороты

В индустрии полупроводниковых процессоров нечасто появляются новые архитектуры набора команд. Последним значительным изменением стало то, что Arm разработала ядра и продала их по лицензии IP, что в одно мгновение изменило подход ведущих производителей того времени к разработке процессоров. Теперь, во время торговых войн и пандемии, доступность расширяемой ISA с открытым исходным кодом, не требующей лицензионных отчислений, оказывается преобразующей и разрушительной силой.

Марк Патрик, Mouser Electronics

Процессор ISA мало изменился за 40 лет

На протяжении десятилетий Intel и Arm доминировали в области архитектуры процессоров. Intel и ее архитектура x86 владеют компьютерной рабочей станцией, рабочим столом и серверным пространством. Тем временем Arm создала более широкий рынок устройств IoT, бытовой электроники и систем промышленной автоматизации.

Ведущие поставщики быстро переходят на архитектуру набора команд RISC-V с открытым исходным кодом (ISA), поскольку клиенты получают коммерческие и технологические преимущества, которые дает подход с открытым исходным кодом. В этой статье мы документируем рождение RISC-V и выделяем некоторые факторы, которые делают его привлекательным. Мы включаем примеры продуктов, уделяем особое внимание оценочным доскам, ресурсам для разработки и растущей экосистеме программных инструментальных средств.

ISA — реальная связь между аппаратным и программным обеспечением процессора

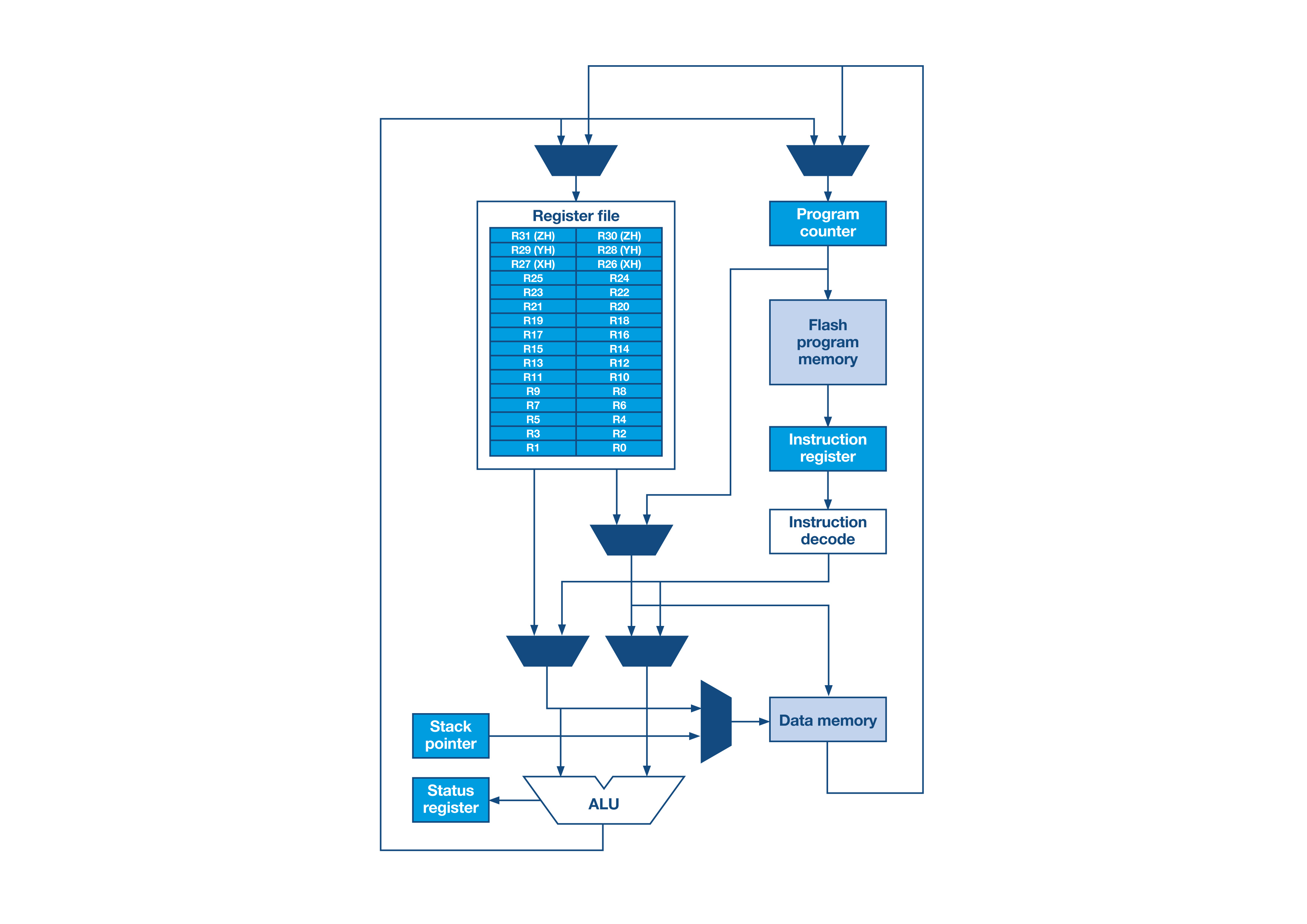

Архитектура набора команд (ISA) обеспечивает интерфейс между мирами программного обеспечения и аппаратным обеспечением процессора. ISA определяет каждый аспект взаимодействия программы с доступным оборудованием, включая арифметико-логический блок (ALU), регистры, память и управляющую логику. Он также определяет длину слова, поддерживаемые типы данных и способ адресации регистров и ячеек памяти. Короче говоря, ISA — это абстракция процессора.

Существует много различных типов ISA, но для большинства практических целей два наиболее важных типа — это компьютер со сложным набором команд (CISC) и компьютер с сокращенным набором команд (RISC). Как следует из названия, CISC содержит множество сложных и специализированных инструкций для различных приложений, некоторые из которых могут использоваться редко. Процессор CISC также имеет множество различных методов адресации и использует инструкции переменной длины. Процессоры на основе CISC дороги в разработке, требуют более сложного программного обеспечения и инструментов программирования, а проектирование занимает значительно больше времени. Примером CISC ISA является Intel x86.

Напротив, процессор на основе RISC намного проще и имеет ограниченный набор часто используемых инструкций, несколько различных режимов адресации и фиксированный размер инструкции. Использование методов конвейерной обработки инструкций позволяет повысить производительность выполнения. В отличие от процессора CISC, который перемещает операнды (значения данных) в память для выполнения вычислений, процессор RISC использует внутренние регистры. Примеры ISA на основе RISC включают Arm, AVR, PIC и MIPS.

Рисунок 1: Пример RISC-архитектуры микроконтроллера Microchip AVR.

ISA — каковы важнейшие факторы успеха?

В оставшейся части этой статьи мы будем рассматривать только процессоры на основе RISC. При ссылке на процессор контекст относится к любому устройству обработки, например микроконтроллерам и микропроцессорам. Популярные RISC ISA доступны с 8-, 16- и 32-битными длинами слов, при этом 64-битные и 128-битные ISA обычно используются для более требовательных и специализированных приложений. Длина слова существенно влияет на конструкцию оборудования, скорость работы процессора и доступный объем памяти.

Как минимум, ISA должен включать арифметико-логический блок, память и управляющую логику. ALU выполняет основные арифметические вычислительные функции, такие как сложение, сравнение и вычитание, с использованием регистров или «немедленно» внутри себя. Адресация памяти может быть абсолютной или индексированной. Логика управления выполняет условное и безусловное ветвление и другие задачи адресации.

Набор команд ISA состоит из кодов операций (машинного кода), которые определяют задачу, которая должна быть выполнена, обычно для операнда (ов). Например, в ISA Atmel / Microchip AVR ADC определяет сложение операндов, содержащихся в двух регистрах, с флагом переноса и помещает результат в регистр назначения. В документации ISA будет указано, сколько тактов или итераций счетчика программ займет каждая инструкция. В процессоре RISC большинство инструкций будет одноцикловым.

Для производителей микроконтроллеров (MCU) и микропроцессоров (MPU) разработка ISA является основным компонентом разработки их продуктов. Таким образом, ISA стали проприетарными, созданными для определенной серии устройств. Примеры включают Atmel / Microchip AVR (8, 16, 32-бит), Microchip PIC (8, 16, 32-бит) и MIPS (32, 64-бит).

Advanced RISC Machines (Arm) сломала традиционную бизнес-модель MCU / MPU в начале 1990-х, когда компания образовалась как дочерняя компания Acorn. Подход Arm пошел по пути лицензирования IP, создавая поток доходов за счет лицензионных платежей, а не за счет изготовления и продажи устройств. Модель Arm быстро стала популярной, освободив поставщиков полупроводников от задачи разработки и переноса их ISA.

Сегодня большинство производителей полупроводников предоставляют процессоры на базе Arm ISA, а некоторые также поставляют устройства на основе их ISA. Каждый платит компании Arm роялти за каждое проданное устройство. Arm контролирует жизненный цикл и текущую разработку ISA.

Хотя у отдельных ISA есть свои плюсы и минусы, успех любой конкретной процессорной архитектуры зависит не только от ее технических достоинств, но и от доступности экосистемы инструментов разработки программного обеспечения. Цепочки инструментов, интегрированные среды разработки, компиляторы, отладчики и промежуточное ПО для конкретных приложений играют жизненно важную роль в росте популярности процессора и его ISA.

Открытый исходный код архитектуры набора команд

Для производителей полупроводников Arm представила стандартную ISA, вокруг которой они могли адаптировать и улучшить параметры периферийного интерфейса устройства для соответствия конкретным приложениям. Такой подход позволил дифференцировать продукцию от других конкурентов полупроводников, также использующих Arm IP. Для установленных ISA, таких как AVR, PIC и т. Д., Широкое распространение Arm уменьшило их общий охват на рынке.

Однако для заказчиков процессоров принятие архитектурного решения о внедрении Arm ISA является благоразумным, поскольку существует несколько поставщиков процессоров, что облегчает выбор вариантов приобретения аналогичных компонентов из второго источника. Стандартизация разработки вокруг определенного набора инструментов также имеет коммерческий смысл.

В отрасли, которая охватила множество концепций с открытым исходным кодом, область архитектуры набора команд процессора выглядела очень закрытой. Так продолжалось до появления RISC-V ISA в 2010 году. Первоначально разработанная в Калифорнийском университете в Беркли как ISA для академических целей, концепция разработки ISA с открытым исходным кодом быстро получила распространение.

Обоснование того, что это открытый исходный код, исходит из мысли, что дизайн ISA мало изменился за последние сорок лет. Если сделать его открытым, это будет способствовать большему взаимодействию и повторному использованию программного обеспечения, что, как мы надеемся, привлечет долгосрочную поддержку со стороны поставщиков инструментальных цепочек. В качестве ISA с открытым исходным кодом поставщики не должны платить никаких лицензионных отчислений и могут создавать новые инструкции и расширения.

Базовая версия RISC-V ISA и связанные с ней расширения разрабатываются и управляются коллективными усилиями академического исследовательского сообщества и промышленности. RISC-V ISA поддерживает длину слова 32, 64 и 128 бит.

В 2015 году в разработке RISC-V был сделан значительный шаг вперед, когда в результате сотрудничества полупроводниковых компаний был основан фонд RISC-V. Привлекательность отсутствия лицензионных отчислений и расширяемости привлекла внимание поставщиков. Лицензиаты Arm не могут настраивать набор инструкций в соответствии с конкретными приложениями — например, с низким энергопотреблением, но лицензиаты RISC-V могут. Фонд RISC-V насчитывает более 750 отраслевых членов.

Поскольку многие крупные поставщики процессоров начали проявлять интерес к RISC-V, сообщество программных инструментов, не желая оставаться в стороне, начало расширять поддержку RISC-V в своих IDE и инструментах.

Начало работы с RISC-V

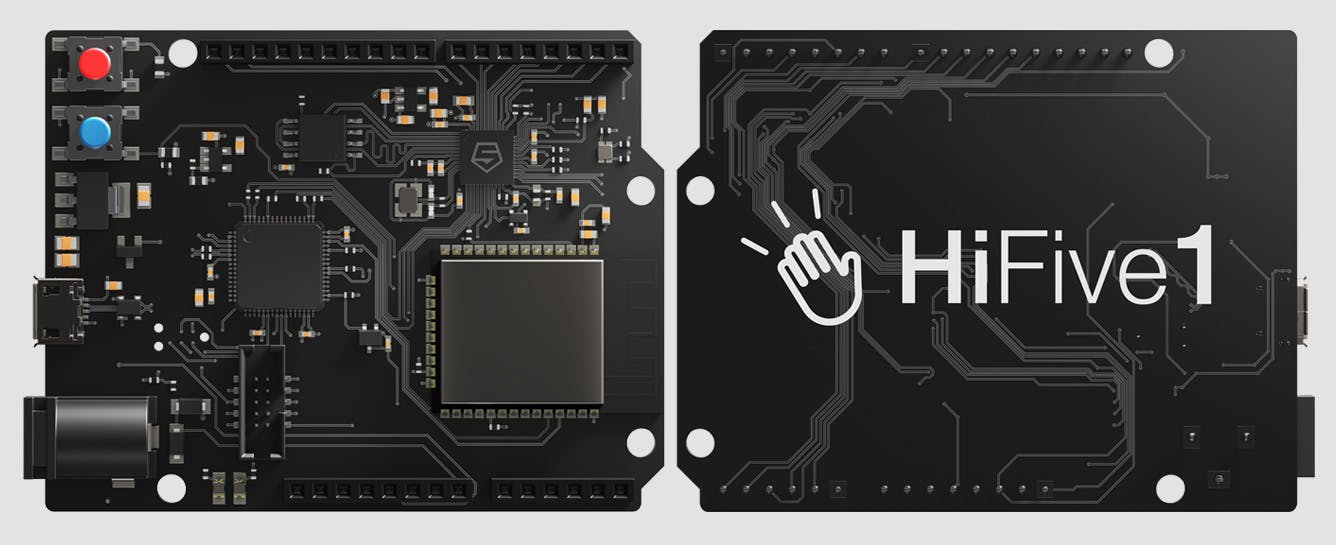

Одним из первых доступных 32-разрядных процессоров на базе RISC-V была SiFive Freedom E31 SoC. SiFive была основана основателями RISC-V ISA и быстро попыталась вывести свой опыт на рынок. Чтобы стимулировать создание прототипа, SiFive краудфандингует недорогую плату для разработки с форм-фактором Arduino HiFive1 . SiFive HiFive1 B включает в себя подключение к Wi-Fi и 32 Мб флэш-памяти.

Рисунок 2: Макетная плата SiFive HiFive1 B.

SEEED также поставляет отладочную плату формата Feather / MKR, Sipeed Longan Nano, оснащенную 0,96-дюймовым ЖК-дисплеем и использующим 32-битное ядро RISC-V GigaDevice.

SparkFun поставляет плату для разработки, аналогичную HiFive1 B. SparkFun RED-V RedBoard также использует форм-фактор Arduino UNO-R3 и SoC SiFive E310 RISC-V.

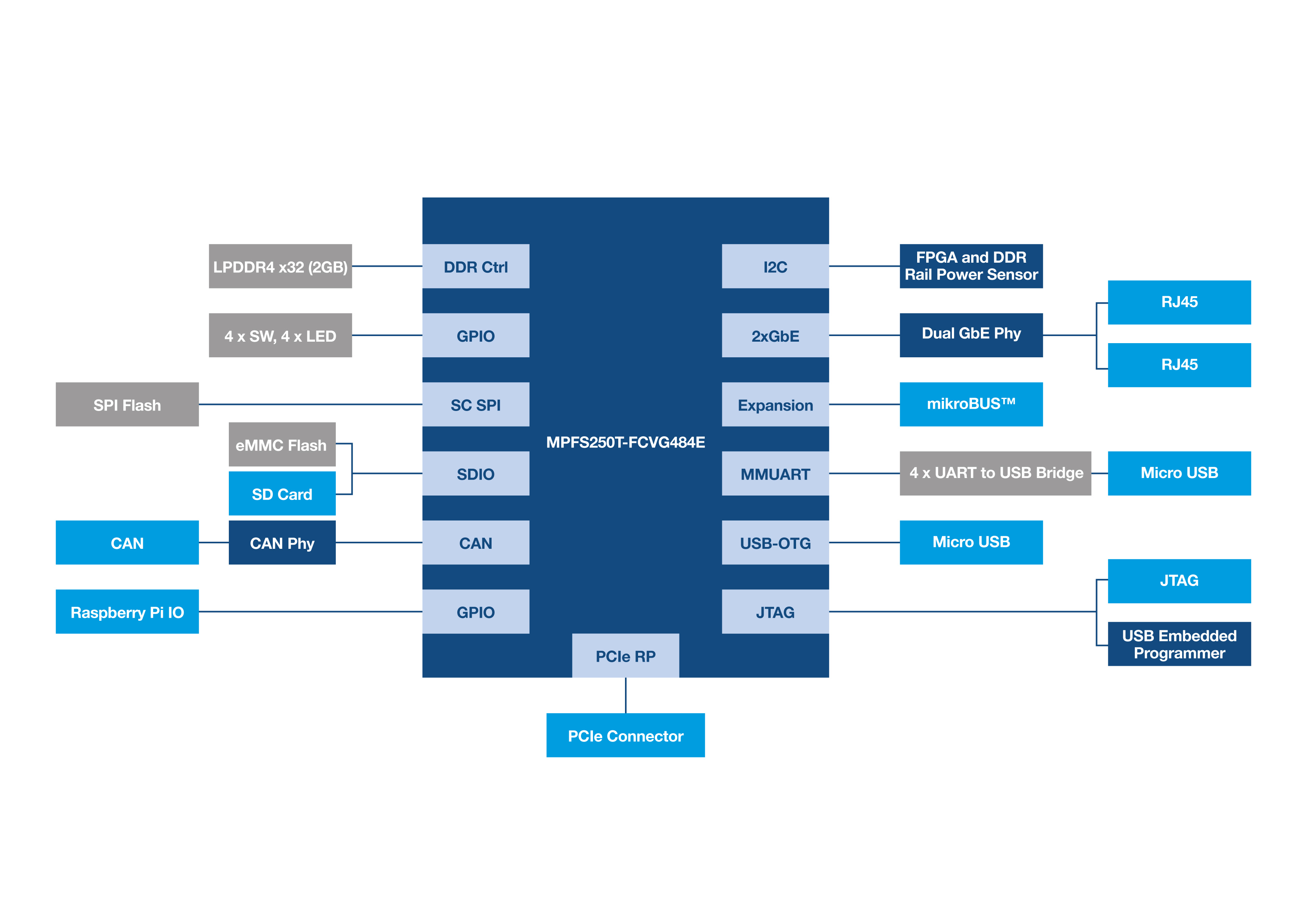

Более комплексная платформа RISC-V, предназначенная для профессиональных инженеров, — это плата разработки Microchip PolarFire SoC FPGA Icicle .

PolarFire SoC, предназначенная для обеспечения оценочной платформы для пятиъядерного ядра RISC-V RV64 с поддержкой Linux, также оснащена 256 КБ логических элементов и 784-элементным математическим блоком. Комплект Icicle хорошо подходит для создания прототипов в режиме реального времени с низким энергопотреблением, от датчиков IoT до приложений машинного обучения, и включает в себя комплексные возможности подключения периферийных интерфейсов, включая HDMI, PCIe, USB, CAN, SPI и I2C. Варианты внешнего интерфейса расширения включают разъем mikroBUS и 40-контактный разъем Raspberry Pi.

Рисунок 3: Функциональная блок-схема оценочного комплекта Microchip RISC-V PolarFire SoC.

RISC-V: впереди

За относительно короткий период времени архитектура набора команд RISC-V набрала значительный импульс. В июле 2020 года Фонд отметил десятую годовщину первоначальной разработки RISC-V. По данным веб-сайта Фонда, в настоящее время коммерчески доступны 12 SoC на основе RISC-V и 86 ядер.

RISC-V быстро зарекомендовал себя как жизнеспособная расширяемая и бесплатная альтернатива другим ISA.